Solved Construct a D flip-flop using a JK flip-flop and some - Chegg

Construct a D flip-flop using a JK flip-flop and some combinational logic. Answer the following questions: a) (3 pt) Using a JK fip-flop with asynchronous active-high clear and trigger by a dock input signal on …

Solved 11.17 Derive the characteristic equations for the - Chegg

Get your coupon Engineering Electrical Engineering Electrical Engineering questions and answers 11.17 Derive the characteristic equations for the following latches and flip-flops in product-of- sums form. …

Solved Here is a D flip-flop for your viewing enjoyment. D Q - Chegg

Here is a D flip-flop for your viewing enjoyment. D Q CLK a) Is this one active on the rising or falling edge? b) Complete the timing diagram. The delay of the flip-flop is "small" compared to the clock …

Solved 1. Design and implement a circuit that operates as a - Chegg

Question: 1. Design and implement a circuit that operates as a binary counter that shouldincrement from 000, 001, ..., 111, and finally roll over back to 000 and repeat the sequence.Use each of …

Solved QUESTIONS Complete questions 1 to 9. 1. List the - Chegg

1. List the synchronous inputs of the D flip-flop. 2. List the asynchronous inputs of the D flip-flop (7474) that you used, 3. List the outputs of the D flip-flop. 4. Which output column in Table 7-4 is exactly the …

Solved Exercise 3.12 Design an asynchronously resettable D - Chegg

Question: Exercise 3.12 Design an asynchronously resettable D latch using logic gates. Exercise 3.13 Design an asynchronously resettable D flip-flop using logic gates.

Solved Chapter 6, problem 5: (10 pts) Considering the - Chegg

Chapter 6, problem 4: (15 pts) For a negative-edge triggered JK flip flop with active-low Preset and Clear inputs (74112), complete each individual timing diagram with the output Q: Chapter 6, problem 7: (10 …

Solved 2. [30 pts] Design a synchronously resettable - Chegg

To start designing a synchronously resettable flip-flop with an enable, create the truth table to specify the behavior of the flip-flop given different inputs for Clk, E, Reset, and D.

Chapter 6, problem 3c.d.e: (5+5+5pts) For the input - Chegg

Assume that the flip flop is a T flip flop with an active low clear and the same inputs as part b. Chapter 6, problem 4: (15 pts) For a negative-edge triggered JK flip flop with active-low Preset and Clear inputs …

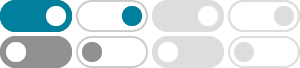

Solved QUESTION 1 A D-type latch is able to change states - Chegg

O flip-flop clear state. Both B and C QUESTION 10 lifference en a an edge-triggered D-type flip-flop is the O triggers on either the rising or falling edge of an ENABLE signal rather than the CLK input logic …